LPDDR6 duplica el ancho de banda de LPDDR5 al alcanzar hasta 38,4 GB/s en un bus de 64 bits, gracias a velocidades de hasta 14,4 Gbps por pin. JEDEC definió este nuevo estándar con una arquitectura renovada que emplea cuatro canales de 24 bits por chip, divididos en subcanales de 12 bits, lo que mejora la concurrencia y reduce la latencia en tareas como inferencia de IA y gráficos en notebooks ultradelgados.

Los dispositivos ahora pueden alternar dinámicamente entre ráfagas de 32 y 64 bytes, lo que les permite equilibrar el consumo de energía y el ancho de banda en tiempo real. Además, los fabricantes introdujeron un nuevo dominio de voltaje (VDD2) y funciones avanzadas de gestión de energía, como el escalado dinámico de frecuencia y voltaje, junto con modos de reposo que reducen el consumo en segundo plano, especialmente útiles en automóviles y dispositivos en el borde de red.

En términos de confiabilidad, los diseñadores integraron funciones como corrección de errores en chip (ECC), paridad de comandos y direcciones, contadores de activación de filas y rutinas de autodiagnóstico. También permiten reservar parte de la memoria para operaciones críticas, lo que facilita su implementación en sistemas de misión crítica.

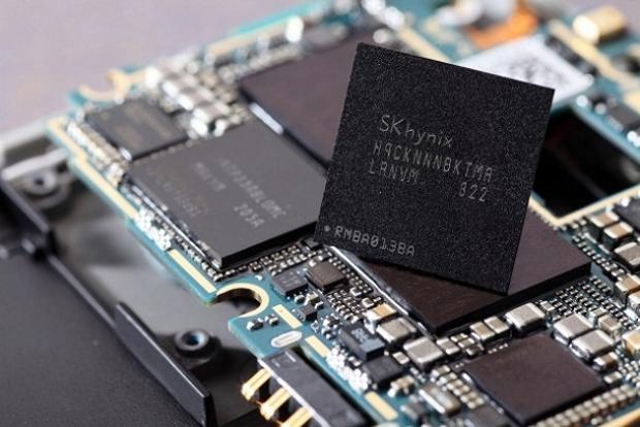

Samsung, Micron y SK Hynix ya están probando módulos entre 4 GB y 64 GB, y comenzarán la producción masiva en el segundo trimestre de 2025. Los primeros equipos que usarán LPDDR6 serán notebooks premium, aceleradores de IA en el borde y sistemas automotrices. Apple, Intel y Qualcomm preparan sus plataformas para aprovechar esta memoria, aunque los teléfonos no tendrán prioridad esta vez.