Los nodos Intel 18A e Intel 14A definen la hoja de ruta de la compañía para alcanzar la fabricación de semiconductores en la escala del Ángstrom. Mientras el 18A introduce la arquitectura de transistores RibbonFET, el 14A implementa la litografía High-NA EUV para mayor densidad. Intel Foundry detalló en X una versión avanzada de la tecnología Foveros para el empaquetado y resguardo físico de estos complejos circuitos integrados.

El empaquetado avanzado es la infraestructura física que protege, alimenta y conecta eléctricamente los bloques de procesamiento que forman un chip moderno. Esta tecnología permite que componentes individuales operen de forma coordinada como una unidad lógica de alto rendimiento.

Visto a escala macroscópica, se puede comparar al rack o chasis y el cableado de un servidor que mantiene unidos los servidores. Sin esta red de soporte, los componentes no podrían intercambiar señales eléctricas ni recibir la energía necesaria para funcionar.

Foveros 3D, EMIB-T y nodos 18A/14A para diseños altamente modulares de Intel

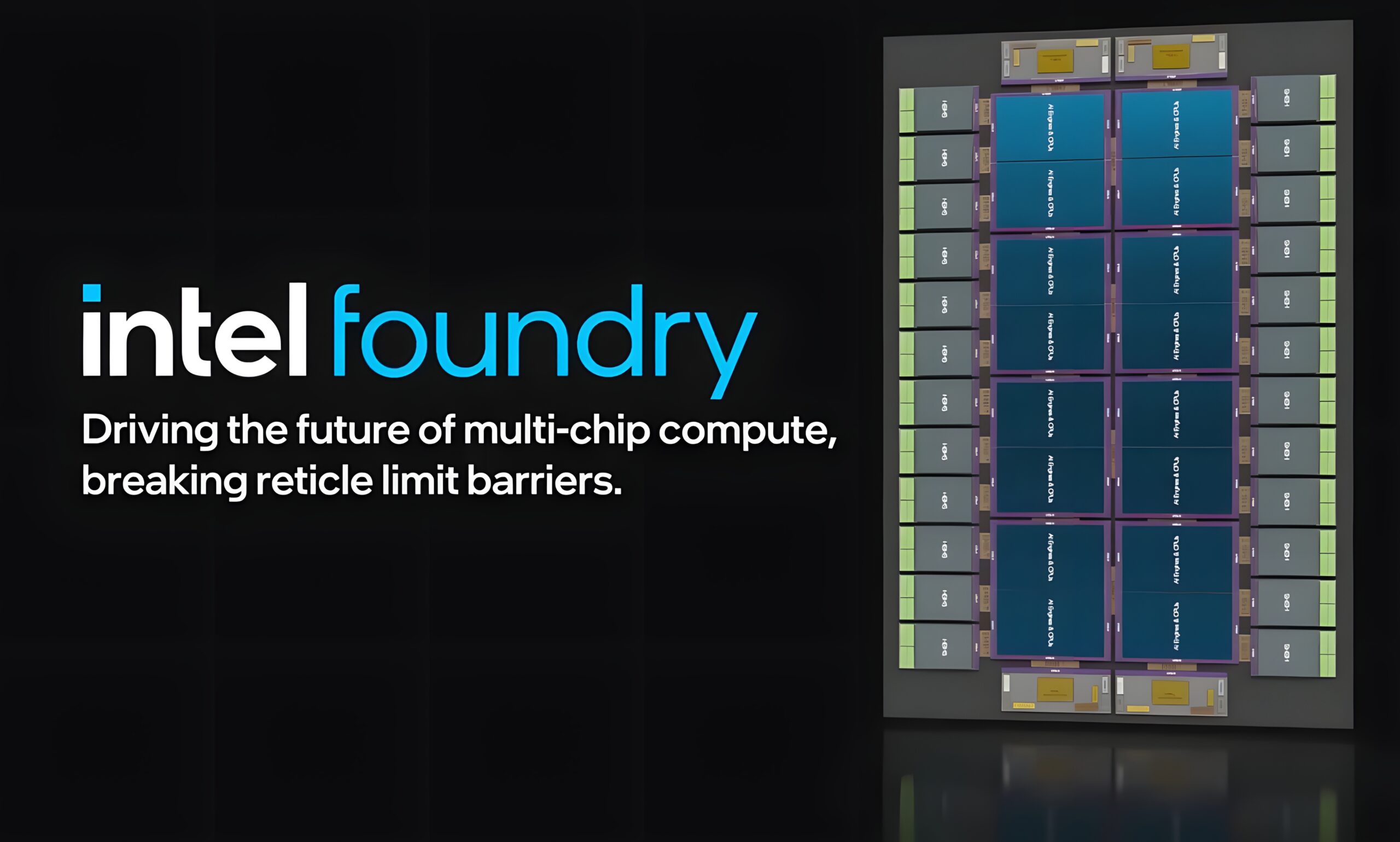

Intel Foundry muestra diseños conceptuales que integran desde cuatro hasta dieciséis mosaicos o tiles de cómputo (módulos o bloques lógicos de procesamiento independientes dentro del paquete) junto a doce o veinticuatro sitios para HBM, además de hasta cuarenta y ocho controladores LPDDR5X en un único paquete.

Además, logra una escalabilidad de retícula superior a doce veces (>12x reticle scalability), que permite superar las limitaciones de tamaño de una única máscara de litografía en un mismo paquete.

En términos simples, la capacidad de crecer gracias a su modularidad se parece a unir varias hojas de plano en un solo esquema continuo, extendiendo el diseño sin quedar limitado por el tamaño físico de una única lámina, literalmente un apilado en 3D.

La estructura parte de un compute base die en proceso 18A-PT que integra SRAM, sobre el cual se apilan mosaicos de cómputo fabricados en 14A o 14A-E mediante Foveros Direct 3D, con unión híbrida de paso ultrafino.

Los distintos chiplets se interconectan mediante EMIB-T, que añade TSV para aumentar el ancho de banda y enlazar los tiles de cómputo con los módulos HBM y las controladoras LPDDR5X dentro del mismo sustrato.

A escala macroscóspica, puede imaginarse como un edificio modular donde cada piso es un tile de cómputo y los pasillos representan EMIB-T, coordinando el flujo de datos y energía entre las plantas y los depósitos de memoria.

En lo lógico, 14A-E introduce RibbonFET 2 y la distribución de energía PowerDirect, mientras que 18A-PT aporta alimentación trasera en el base del die para mejorar densidad lógica y confiabilidad del suministro eléctrico.

En términos de memoria, Intel plantea compatibilidad con estándares actuales y futuros de HBM para dar flexibilidad a los diseñadores de aceleradores de IA y HPC. Puedes revisar más detalles en el video publicado por Intel en X que te mostramos anteriormente.