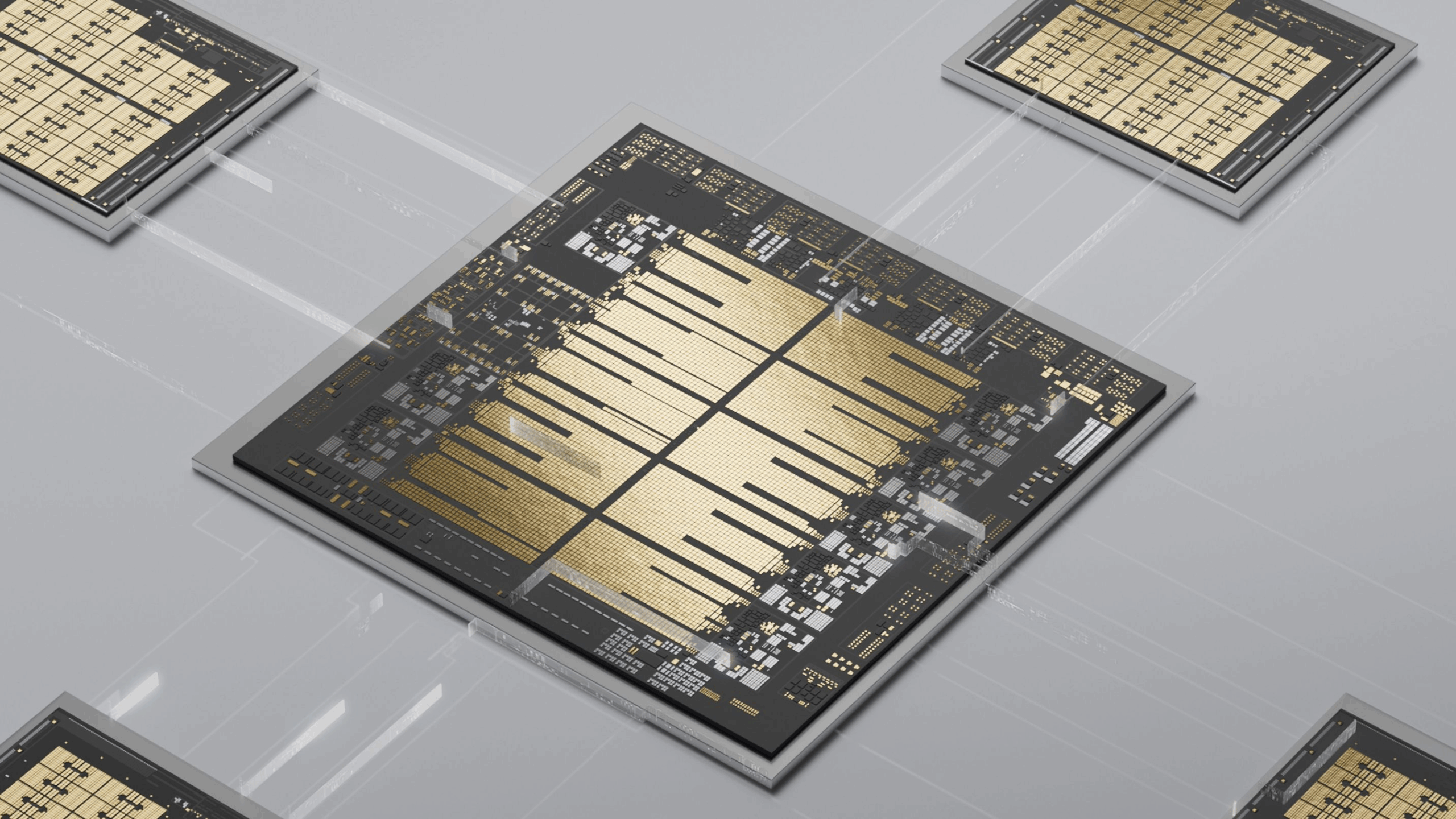

En el marco de la cita Hot Chips 2024, IBM presentó un nuevo procesador Telum II, que es una mejora sustantiva a su antecesor lanzado en 2021 y también el Acelerador IBM Spyre.

IBM Telum II está diseñado para desempeñarse en plataformas IBM Z e IBM LinuxONE, cuyo foco principal es mejorar el rendimiento mediante mejoras esenciales en materia de frecuencia, cache, arquitectura E/S y aceleración de IA en el chip.

Spyre fue el segundo anuncio de IBM, que llega a complementar la arquitectura para IA que plantea el gigante tecnológico. Cuenta con 32 núcleos de IA y una arquitectura alineada con los aceleradores integrados en Telum II. Esta configuración permite un sistema escalable en capacidad en inferencia (razonamiento).

¿Qué mejoras trae el procesador Telum II frente a su antecesor?

Las mejoras que trae el procesador Telum II están enfocadas en materias de IA, y en optimizar las integraciones complejas de cargas de trabajo.

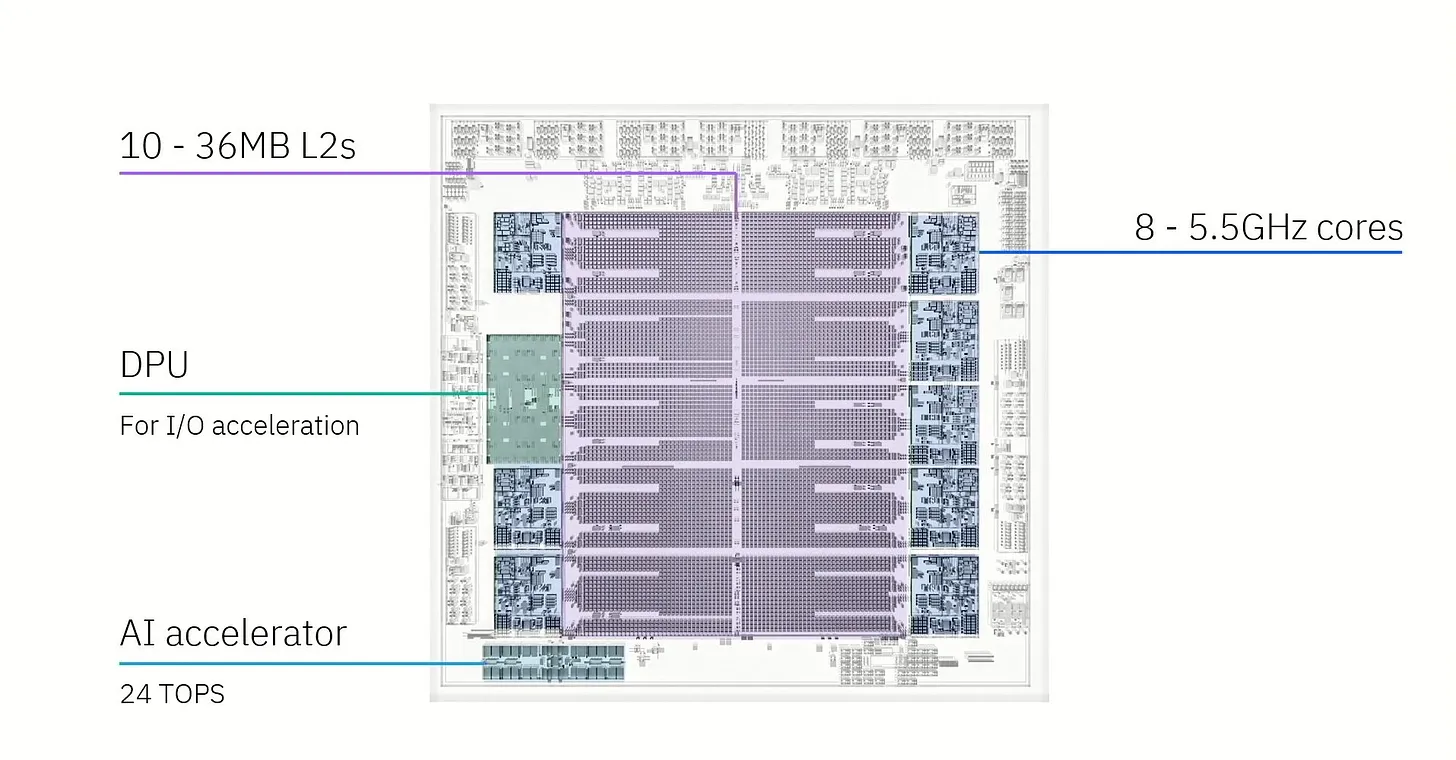

El Chip fue creado con tecnología de 5nm de Samsung, y considera 8 núcleos de 5.5GHz, y un aumento del 40% del cache en el chip, junto con nuevas unidades para acelerar la entrada/salida de datos y procesar modelos de IA directamente en el procesador.

Otro de los aspectos interesantes del chip de IBM, es la capacidad de inferencia, cuadriplicando la potencia respecto a su antecesor y alcanza 24 TOPS por acelerador. Esto se complementa con soporte para INT8, nuevas primitivas de cómputo para modelos de lenguaje.

En cuanto al Acelerador IBM Spyre amplía esta capacidad con 32 núcleos de IA y se conecta mediante PCIe al subsistema de E/S, permitiendo una escalabilidad importante.

La conjunción entre el Telum II y Spyre están pensandos para que ejecuten modelos de IA para detección de fraude, al combinar redes neuronales con modelos de lenguaje extensos.

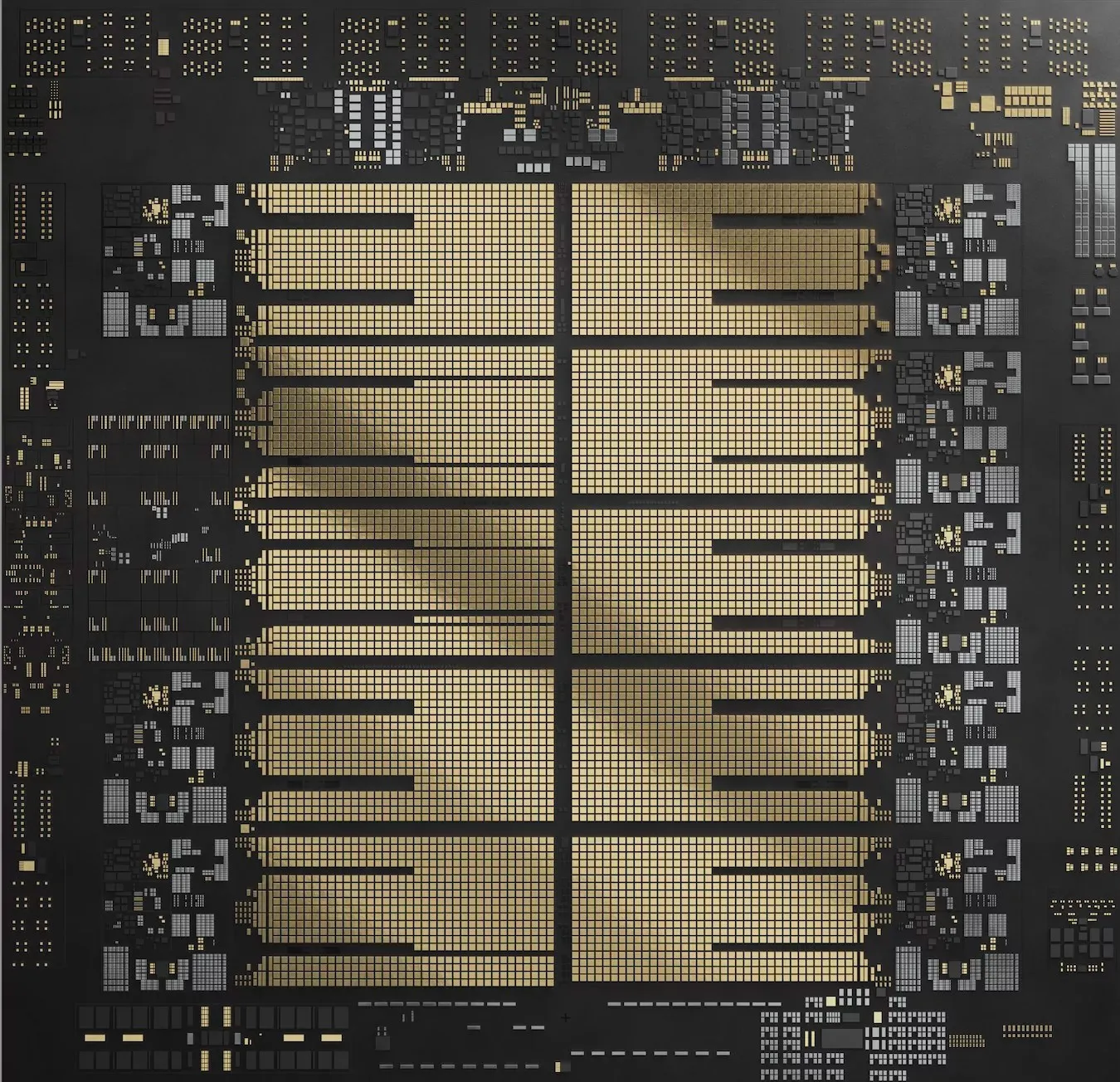

¿Cómo está construido internamente el chip de IBM?

El Chip IBM Telum II está construido con una arquitectura modular simétrica, donde el chip se compone en diez bloques iguales, organizados en una malla, donde cada bloque integra un núcleo de CPU de alto rendimiento junto a 36 MB de caché L2.

Según IBM, esta configuración está ideada para que trabaje de manera autónoma, pero en completa sincronía, para mantener una muy baja latencia y alta eficiencia bajo cargas de trabajo intensas.

IBM ha definido que este nuevo chip no cuente con una caché L3 física dedicada, sino que ha implementado caché L3 virtual distribuida entre los bloques.

La firma destaca que cuando una línea de caché L2 se desocupa, puede ser enviada a otro bloque con menor saturación, facilitando así el uso total de la memoria disponible en el chip. Esta estrategia se extiende a nivel de sistema para formar también una caché L4 virtual, compartida entre múltiples chips o cajones conectados.